文章编号:1671-6833(2012)06-0010-05

# 时序逻辑电路在片进化设计与实现

娄建安<sup>1</sup>, 李川涛<sup>1</sup>, 常小龙<sup>2</sup>, 满梦华<sup>2</sup>

(1. 军械工程学院 电气工程系,河北 石家庄 050003; 2. 军械工程学院 静电与电磁防护研究所,河北 石家庄 050003)

摘 要: 针对 EHW (Evolvable Hardware) 技术在电子设计自动化、容错运行、自诊断、自适应和自修复等方面的特点,借鉴传统时序电路设计的方法,建立了适应于片内进化的时序电路演化模型和基于 Xilinx FPGA Virtex -5(XC5VLX110T)的 Microblaze 软核结构,并运行 GA 算法对本文设计的 VRC 进行配置、演化.进而,利用设计的时序电路演化模型成功演化了 1001 检波器以及二、四、八分频器等时序逻辑电路,验证了本模型的有效性、通用性,并深入分析了演化算法中的随机数种子对演化性能的影响,可为演化算法设计提供一定的参考.

关键词:时序逻辑;演化;在片电路;Microblaze

中图分类号; TP 302.1

文献标志码: A

doi:10.3969/j. issn. 1671 - 6833.2012.06.003

#### 0 引言

演化硬件技术可根据环境变化改变电路内部结构,从而实现电子电路的结构自组织、环境自适应以及故障自修复功能<sup>[1]</sup>.全世界有许多机构进行了演化硬件的研究,并且成果丰硕,特别是姚新、Higuichi等学者提出了基于 FPGA 结构可重配置特性的 EHW 具体实现方法,将研究进程大大加速<sup>[2]</sup>.之后,演化硬件在理论研究和工程应用方面均发展迅猛.其中,在电路容错运行和自修复方面,满梦华等<sup>[3]</sup>利用演化硬件技术实现了逻辑门单元在线自修复;在图像处理方面,王珑等<sup>[4]</sup>将演化硬件技术应用到了图像加密技术中;在信号传输和处理方面,Faleoner等<sup>[5]</sup>使用内部型可进化硬件完成了高速数据线的信号完整性检查.

## 1 时序逻辑电路演化模型设计

电路演化设计的关键在于设计结构可重构的 电路演化模型,利用演化算法不断变化电路结构 从而实现目标功能.但目前此类研究多以加法器、 乘法器等组合电路为对象,而时序电路的研究相 对较少<sup>[6]</sup>.其主要原因在于时序电路内部存在反 馈连接,使得电路的染色体编码更为复杂,而且, 验证测试评估困难,进化成功率较低,仿真速度缓 慢.有鉴于此,笔者专门设计并实现了一种通用的 时序电路演化模型.

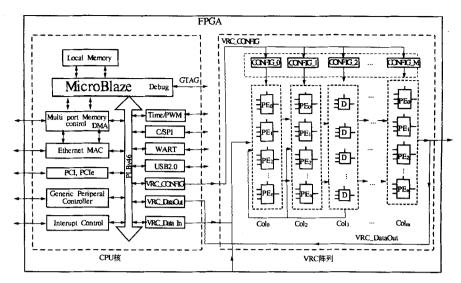

## 1.1 硬件演化平台构建

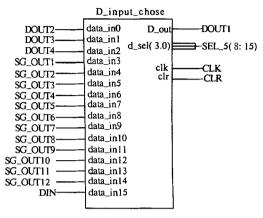

硬件进化平台主要包括基于 Microblaze 软核的 CPU 设计、可重构数字电路网络模型设计两部分内容. Microblaze 软核的主要功能是运行 GA 算法,进行 VRC(Virtual Reconfigurable Circuit)矩阵演化. Microblaze 软核可以根据实际需要予以裁剪,其 GPIO 的数目不限,对 VRC 的配置都是全并行的. 如串口、DMA 控制器、CAN 控制器等诸多外部设备,均可十分方便地通过选择而增删. 而并行配置方式最大的优点就是 VRC 配置速度快,不仅可以提高演化速度,而且设计简单;它的缺点是演化电路的规模不易直接扩充,如图 1 所示.

#### 1.2 时序逻辑电路的全向连接演化模型

图 1 中的 VRC 演化模型主要由两部分组成,即逻辑组合电路和 D 触发器组. 逻辑组合电路是由 m×n个 PE(Programmable Element)单元构成的阵列,PE 单元的运算结果只能前馈输出到下一列. D 触发器组的输出既可以前馈也可以反馈,于是整个电路就可以成为一个全向连接的网络. 实验证明这种全向连接的方法对于提高电路的演化速度和成功率都有非常大的帮助.

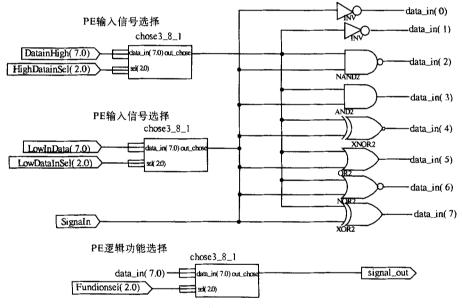

PE 单元是 VRC 演化模型的基本元素. 其结构设计对电路的演化的成功率和演化算法的收敛速度都有很大的影响, 其结构如图 2 所示.

收稿日期:2012-06-12;修订日期:2012-08-01

基金项目:国防科技重点实验室基金项目(9140C8702020803)

作者简介:娄建安(1967-)男,河南漯河人,军械工程学院教授,博士,主要从事智能检测、故障诊断、演化硬件等研究,E-mail:zxs\_lja@sina.com.

图 1 硬件讲化平台内部模块

Fig. 1 Internal module of evolution hardware platform

图 2 组合逻辑可编程单元

Fig. 2 Programmable combinational logic unit

PE 中包含 AND、OR、NOT 以及 XOR 等基本单元,以便构成各种复杂的组合电路功能.同时,PE 还添加了 NAND、NOR 以及 NXOR 等逻辑门,一旦用到时可以直接调用而不必通过基本单元的合成,以提高电路的演化速度,但是用不到时会降低 FPGA 内部逻辑资源的使用率.矩阵中每个 PE单元相互连接构成功能电路时,只会选择上述其中一种逻辑门作为自己的运算功能.

图中的 chose\_3\_8\_1 为 8 选 1 多路选择器,从 上到下其功能依次为输入选择、输出选择和功能 选择. DataInHigh 为该层单元的一个 8 输入数据. 这 8 个数据可能来自 VRC 的输入,也可以为上层 PE 的输出,或者为前层或者后层保存电路的输出. HighDataInSel 端口为输入选择信号,选择该PE 的输入为 DataInHigh(7:0)中的某一个. Functionsel(2:0)为功能选择端口,选择使用某一个逻辑门,端口 signal\_out 为该 PE 的输出.

用 PE 可以组成一个可编程功能的矩阵.该矩阵中存在大量冗余且可编程的资源,所以实现同样功能的目标电路可以有多种结构形式.当有个别或相对较少的单元受损之后,通过重新配置电路结构,完全可能避开损伤部分,从而使得该矩阵仍然可以继续正常工作,即具有了容错运行和自修复的功能.

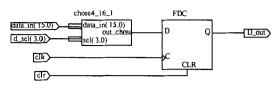

时序逻辑电路内进化模型中必须有电路保存的部分,其结构如图 3 所示.

图 3 电路保存部分

Fig. 3 Circuit's temporary part

元件 Chose4\_16\_1 是 16 选 1 的多路选择器, 控制信号为 4 位,通过该元件选择 D 触发器所要 保存的数据.端口 clk 和 clr 分别为时钟信号和 D 触发器清零信号,在同步时序组合逻辑电路中,所 有 D 触发器的 clk 和 clr 均连接在一起. D\_out 的 输出既可当做整个 VRC 的输出,也可做下层 PE 单元的输入或者上层 PE 单元的输入,即保存部 分输出,使其既可反馈,也可向前传输.

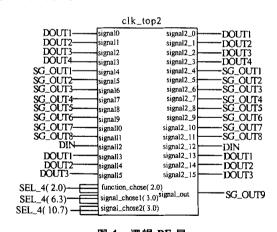

## 2 演化模型在 ISE 开发环境中的实现

在本文的 VRC 模型设计中,选择了原理图和 VHDL 代码相结合的方式设计.需要逻辑转换的部分用 VHDL 代码编写,如多路选择器.而在图形化显示更容易理解的地方,采用原理图编辑的方法设计.笔者设计的内进化 VRC 分别由 12 个如图 4 所示的逻辑 PE 层和 4 个如图 5 所示的保存 PE 层构成.

图 4 逻辑 PE 层 Fig. 4 Logic PE layer

如图 1 所示,12 个逻辑 PE 层在前,4 个保存 PE 层在后,共 16 列. 第  $n(n \le 12)$  列可以接受 Microblaze 输出、保存 PE 层的输出、第 m(m < n) 列逻辑 PE 输出和 FPGA 管脚的信号作为输入. 第 n(n < 13) 列可以接受 Microblaze 输出信息、FPGA 管脚的信号、 $m(m \ne n)$  列的输入信息或者输出信息作为输入.

演化阵列的列数要结合所要演化的目标电路的规模大小而设定. 若阵列规模过小,目标电路可能演化不出来,而规模太大则演化时间可能过长. 本设计中,所演化的电路都是以分为时间单位,一般目标电路的演化都不会超过 10 min. 在目标电路难以确定的情况下,可以尽量扩大演化层数.

图 5 保存 PE 层 Fig. 5 Temporary PE layer

# 3 时序逻辑电路演化算法和演化结果分析

时序逻辑电路在片进化设计的过程有两个关键.一是在线进化设计目标电路,CPU利用遗传算法不停地改变电路结构编码,利用编码配置VRC演化阵列,直至满足目标电路要求.二是目标电路的配置,寻找到目标电路后,把该电路对应的染色体编码重新配置VRC阵列,最终形成正确的目标电路.当外部环境变化导致VRC不能正常工作或任务变更时,两者之间重新建立通信,运行进化算法,对目标电路进行演化,直至满足功能要求.

#### 3.1 演化算法

目标电路的搜索采用遗传算法.遗传算法是通过模拟自然进化过程搜索最优解的方法,包含选择、交叉、变异等基本操作.本实验采用经典的(1+λ)演化策略,实现的步骤如下:

(1)根据 VRC 结构确定配置编码的格式和长度. VRC 的配置编码为一长串二进制数,由 VRC 的第一列开始编码到最后一列组成如" $b_1$   $b_2$   $b_3$   $b_4$   $b_5$   $b_6$ … $b_n$ ", b 为 1 或者 0,其中 n 为配置编码的总位数. 配置编码的排列遵循 PE 单元的排列,如  $b_1b_2b_3$  代表第一层 PE 的功能配置位, $b_4b_5b_6$  代表第一层 PE 左侧的输入信号选择, $b_7b_8b_9$  代表第一层 PE 右侧的输入信号选择……, $b_{146}b_{147}b_{148}$ 代表最后一层的左侧信号输入选择.

(2)初始化种群. 在初始化种群的过程中需要注意的有两个方面. 一方面是随机数种子的选

择,经验证明随机数种子对演化代数的影响非常大.第二是结合具体的 VRC 设计,在利用随机数初始化种群之后,需要适当的修改,如第一层 VRC 的输入端必需有外部输入或者来自 FPGA 管脚的输入.

- (3)寻找最优个体. 将种群的编码配置到 VRC 当中去,根据目标电路确定目标输入数组 M 与其对应的目标输出数组 N,给 VRC 输出目标输入数组 M,读取输出数组 I,将数组 I 与数组 N 比较,相同的值越多则说明适应度越高. 如果全部相同则停止演化.

- (4)变异. 令种群个数为 n,利用找到的最优个体变异出(n-1)个新个体.

- (5)交叉. 令种群个数为 n, (n-1)个新个体之间进行交叉.

- (6)生成新种群. 删除适应度最低的个体,并用最优个体替换掉最差个体结合 4,5 步生成的 (n-1)个新个体,生成当前种群;返回到第 3 步.

#### 3.2 结果分析

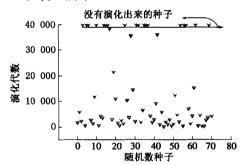

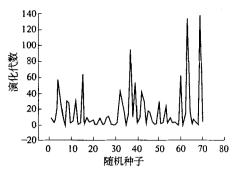

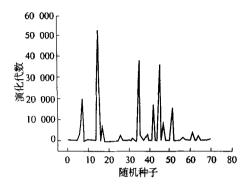

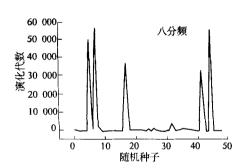

利用上述硬件演化平台、演化模型和遗传算法,分别演化了1001序列检测器、二分频、四分频以及八分频等电路,相应的演化代数分布情况如图 6~9 和表 1 所示.

图 6 演化 1001 序列检测器

Fig. 6 Sequence detector evolution

图 7 演化二分频电路

Fig. 7 Divide by two circuit evolution

图 8 演化四分频电路

Fig. 8 Divide by four circuit evolution

图 9 演化八分频电路

Fig. 9 Divide by eight circuit evolution

表 1 不同目标电路的演化数据统计

Tab. 1 Statistics of difference target circuit evolution

| 目标电路 | 最大演化代数  | 最小演化代数 | 平均演化代数 | 标准差     | 演化成功率/% |

|------|---------|--------|--------|---------|---------|

| 二分频  | 137     | 0      | 16     | 28      | 100     |

| 四分频  | 51 949  | 0      | 3 020  | 9 079   | 100     |

| 八分频  | 561 645 | 26     | 48 658 | 140 832 | 100     |

| 序列检测 | 40 000  | 120    | 14 716 | 16 655  | 74      |

可以看出,设计的演化模型能够成功演化多种时序电路.演化的成功率证明,该模型特别适宜于演化分频器电路.遗传算法执行时,需要利用伪随机数发生器初始化种群.在实验过程中发现,伪随机数的种子对电路演化的收敛速度有十分重要的影响.为此,分别将随机数种子从1到70依次进行了电路演化.种群的规模大小为5,变异

率<sup>[7-8]</sup>都是用 0.01,每个随机数对应的演化时间 均未超过 10 分钟.需要说明的是,演化 1001 检波 器时,其演化成功率为 74%.但是当随机数种子 为 73 时,演化代数只需要 135 代.与此相同,在演 化分频电路时,不同的种子演化速度差别亦很大. 因此,在实际演化电路时可以参照本实验结果选 取适当的随机数种子来初始化种群,提高电路演 化的收敛速率.

## 4 结论

随着嵌入式技术的发展,更多的电子系统都需要脱离 PC 机运行,笔者只用一片 FPGA 实现了片内运行演化算法和实时配置全向连接的 VRC 矩阵.通过改变遗传算法,利用同一个模型实现了二分频、四分频、八分频和序列检测器,验证了本模型的通用性.由于时序电路的输出不仅取决于当前的输入也与前一个状态相关,所以其研究难度大,笔者结合其电路中间状态有限的特点,成功的解决了这个问题.时序逻辑电路利用演化硬件技术设计的研究较少,笔者详细论述并实现了时序逻辑电路在片演化,将有效扩展演化 EHW 技术的应用范围.

## 参考文献:

- [1] 刘尚合,原亮,褚杰. 电磁仿生学——电磁防护研究的新领域[J]. 自然杂志, 2009, 31(1): 1-7.

- [2] YAO Xin, HIGUCHI T. Promises and challenges of evolvable hardware [J]. IEEE Trans on Systems Man and Cybernetics-Part C: Applications and Reviews, 1999, 29(1): 87-97.

- [3] 满梦华,原亮,巨政权.嵌入式系统门级在线自修复

- 技术研究[J]. 计算机工程,2011,37(19):9-11.

- [4] 王珑,李元香,金彤. 基于演化硬件的图像加密技术研究[J]. 计算机科学与工程,2009,31(12):31-34.

- [5] FALEONER M C, KAMISETTY K, NORMAN A, et al. Using evolutionary algorithms for signal integrity checks of high speed data buses [C]//Proceedings of the 2007 IEEE Workshopon Evolvable and Adaptive Hardware (WEAH 2007). Honolulu Hawaii: IEEE press, 2007:35-39.

- [6] ALI B, ALMAINI A E A, KALGANOVA T, et al. Evolutionary algorithms and their use in the design of sequential logic circuits [J]. Genetic Programming and Evolvable Machines, 2004(5): 11-29.

- [7] STOMEO E, KALGANOVA T, LAMBERT C. Mutation rate for evolvable hardware [C]// Proceedings of World Academy of Science, Engineering and Technology. [S. 1.]: World Academy of Science Engineering and Technology, 2005:117-124.

- [8] KEYMEULEN D, STOICA A, ZEBULUM R, et al. Self-reconfigured mixed - signal integrated circuits architecture comprising a field programmable analog Array and a general purpose genetic algorithm IP core [C]//ICES. [S. 1.]; [S. n.], 2008; 225 - 236.

### Design and Implementation of Sequential Logic Circuit Evolution on Chip

LOU Jian-an<sup>1</sup>, LI Chuan-tao<sup>1</sup>, CHANG Xiao-long<sup>2</sup>, MAN Meng-hua<sup>2</sup>

(1. Department of Electrical Engineering, Ordnance Engineering College, Shijiazhuang 050003, China; 2. Institute of Electrostatic and Electromagnetic Protection, Ordnance Engineering College, Shijiazhuang 050003, China)

Abstract: EHW (Evolvable Hardware) technique has the advantages of fault tolerant operation, self diagnosis, adaptive and self repairing, so it has high application value in electronic automation design. Sequential logic circuit as a part of evolvable hardware has the problem of multiple states and the fitness function in the implementation, and is not easy to build. In this paper, based on existing studies and traditional sequential circuit design method, we developed sequential logic circuit evolution model, and in the Xilinx FPGA Virtex-5 (XC5VLX110T) established the Microblaze core running GA algorithm for the VRC configuration and evolution. In the same model, by changing the GA program we also designed "1001" detectors, two, four, eight frequency divider. So it successfully demonstrated the validity and versatility of the model. The experiment was in-depth analyzed the evolution performance with random seeds, and provided a reference for the further design.

Keywords: sequential logic; evolution; on chip circuit; Microblaze